임석구, 홍경호의 '최신 컴퓨터 구조' 를 참고 하였습니다.

1. 제어 장치의 기능

2. 제어 장치의 종류

3. 명령어 사이클

4. 파이프 라이닝

1. 제어장치의 기능

제어장치

정의 : 컴퓨터의 모든 동작을 제어하는 CPU의 핵심장치

기능

1. ALU, I/O 장치를 제어해 프로세스가 명령한 수행

2. 주기억 장치의 명령어를 읽어 CPU의 명령 레지스터 IR로 가져오고, 이의 opcode를 해독하여 제어 신호를 발생

(명령어 인출, 해독, 실행 제어)

2. 제어장치의 종류

- 하드와이어 제어장치

- 마이크로 프로그램 제어장치

- 수평적 마이크로 프로그램

- 수직적 마이크로 프로그램

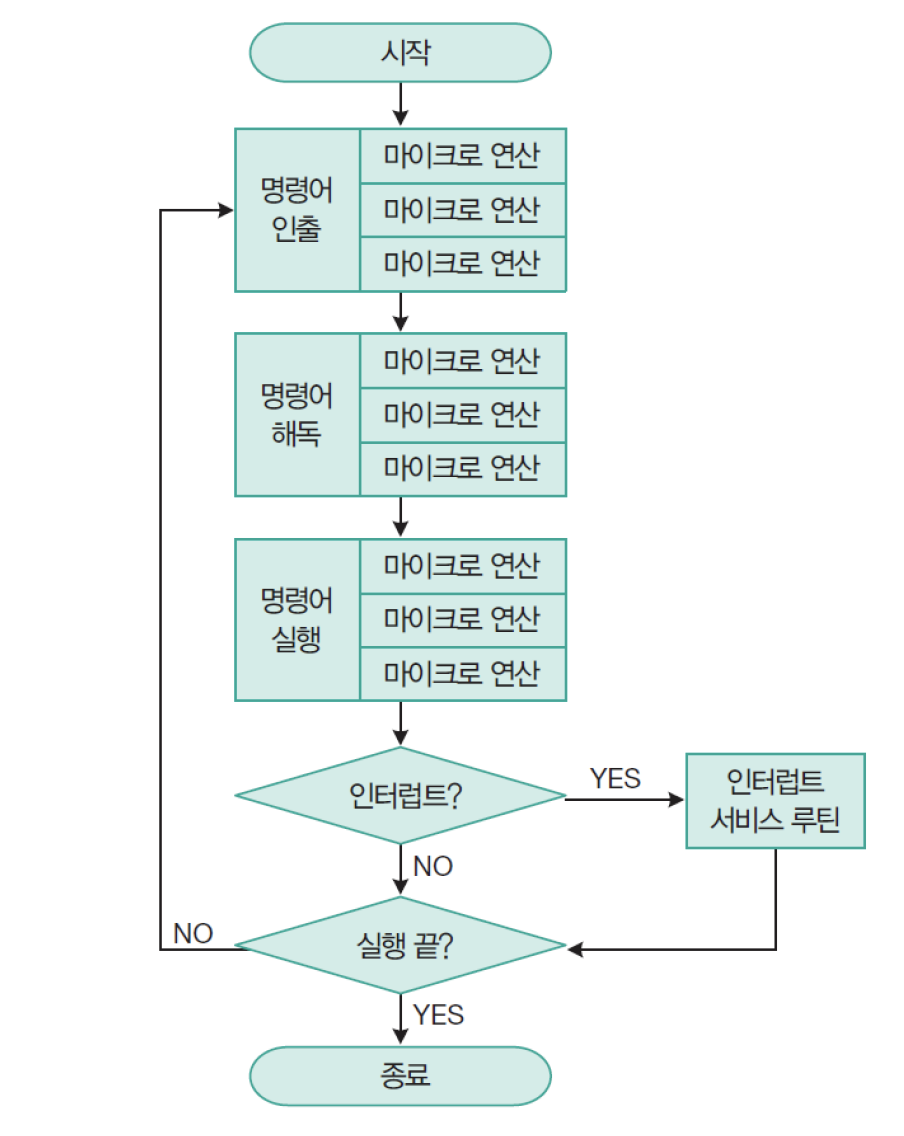

3. 명령어 사이클

명령어 사이클 : 명령어 인출 -> 명령어 해독 -> 명령어 실행

인터럽트 사이클 : 매 명령어 사이클이 끝나고 인터럽트 유무를 점검, 있으면 인터럽트 루틴 실행

마이크로 연산 : 프로세서의 가장 작은 동작

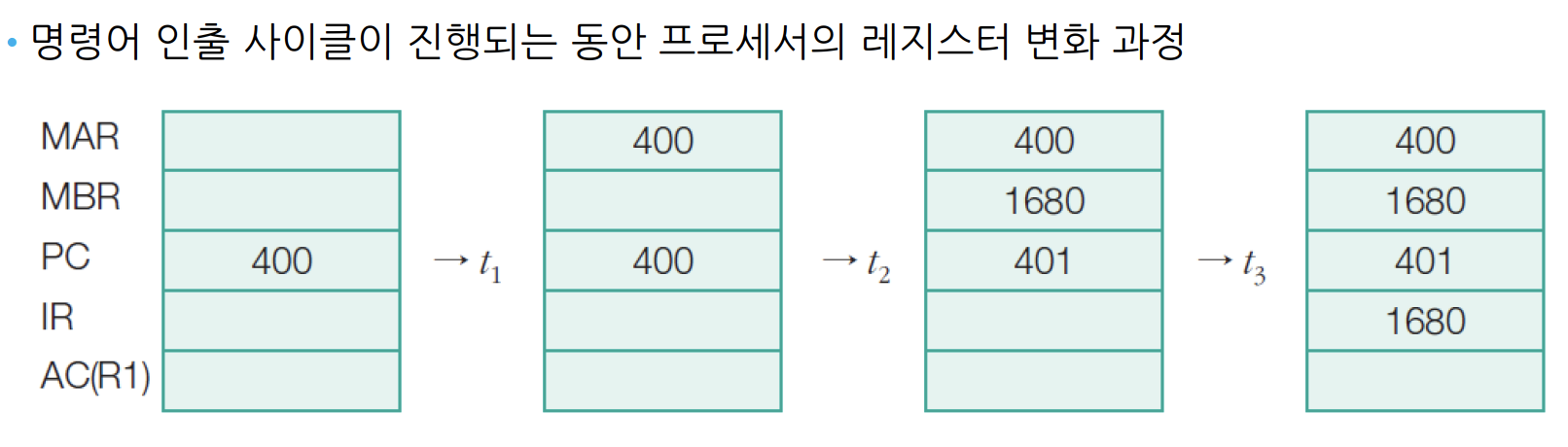

3-1. 명령어 인출 사이클

- 다음에 실행할 명령어를 주기억장치로 부터 읽어오는 과정

- PC로부터 주소를 읽고 주기억장치의 해당 주소로 가서 데이터를 읽어 명령 레지스터(IR)로 가져오는 과정

마이크로 연산 설명

t1 : MAR <- (PC)

t2 : MBR <- M[MAR], PC <- (PC) + I

-> MAR은 주소버스를 통해 주기억장치에서 명령어를 읽고 데이터버스를 통해 해당 주소의 값을 전달

-> I는 명령어의 크기로 바이트 단위이며 t2 또는 t3시점에 PC 증가

t3 : IR <- (MBR)

3-2. 명령어 해독 사이클

1. 명령 레지스터(IR)의 내용 중 opcode만 해독기로 전달

2. 해독기는 제어 기억장치에서 명령 연산에 해당되는 마이크로 루틴을 찾아 해독

마이크로 연산 설명

t1 : Decoder <- (IR : opcode)

t2 : Instruction Decoding

-> 디코더는 명령어를 CU에 전달하고 CU는 명령어를 해독하여 제어신호를 발생시킨다.

3-3. 명령어 실행 사이클

- 해독된 명령어를 실행하는 사이클

예시 1 : 데이터를 읽어서 레지스터 R1에 저장하는 명령어 사이클

(주기억 장치에 있는 데이터를 읽어서 R1에 저장하는 과정)

MAR <- (IR : operand)

MBR <- M[MAR]

R1(누산기) <- MBR

- (b)에서 IR은 MAR로 operand인 860전달

- (c)에서 주기억장치의 주소 860에 해당하는 데이터 5를 MBR로 전달

- (d)에서 5를 R1으로 전달

예시2 : ADD

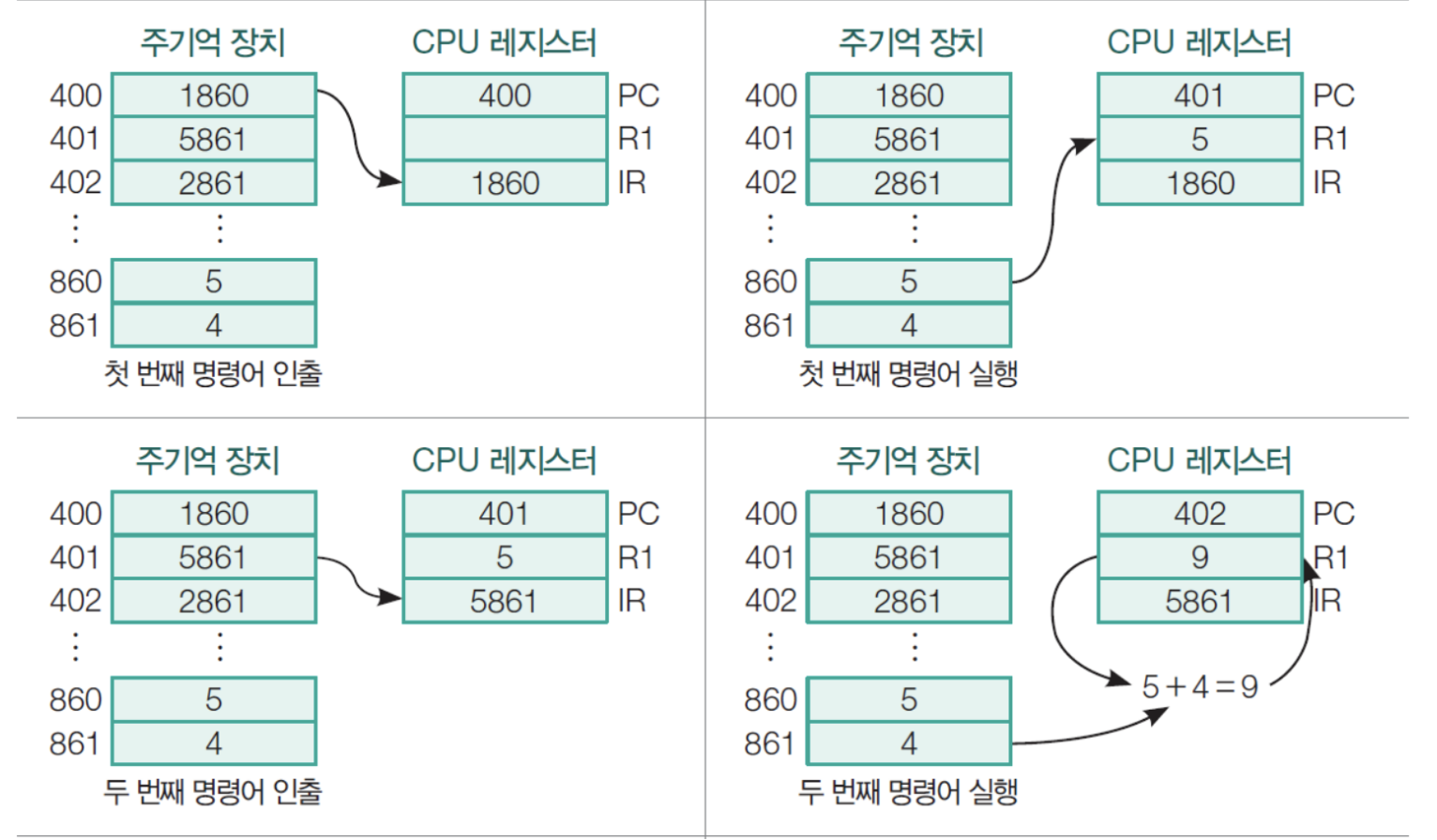

예시3 : LOAD(1), ADD(5), STORE(2)

LOAD(1)

인출 : PC는 MAR로 400을 전달하고 MAR은 주기억장치의 주소 400에 해당하는 값 1860을 가져와 MBR을 거쳐 IR로 전달, 이 후, PC는 명령어 크기만큼 증가

실행 : 1860에서 860에 해당하는 값을 MAR, MBR을 거쳐 주기억 장치에서 인출해 R1에 저장

ADD(5)

인출 : PC에서 가져온 주소 값 401에서 값을 가져와 IR로 전달 이 후, PC는 명령어 크기만큼 증가

실행 : 5861에서 861에 해당하는 값을 가져와 R1에 가져오는데 기존 값에 더해서 저장

STORE(2)

인출 : PC에서 가져온 주소 값 402에서 2861을 가져와 IR에 전달 이 후, PC는 명령어 크기만큼 증가

실행 : 주소 861에 R1의 값 9를 저장.

예시 4 : ISZ(Increment and Skip if Zero)

ISZ X : X의 값을 증가시키고 그 결과가 0이면 바로 다음 명령을 건너뜀

t1 : MAR <- (IR : X)

t2 : MBR <- M[MAR] + 1

t3 : M[MAR] <- (MBR), IF((MBR) = 0) then (PC <- PC + I)

예시 5 : BSA(Brach-and-Save-Address)

t1 : SP의 값을 MAR로 보내고 PC의 값은 MBR로 보내놓는다.

t2 : MBR의 값을 MAR에 지정된 주소에 저장. 즉, 결과적으로 PC의 값이 SP값에 해당하는 주소에 저장, SP는 명령어 크기만큼 감소

t3 : PC에는 IR의 값(550) 배치

예시 6 : RET(Return)

t1 : SP를 명령어 크기만큼 증가

t2 : MAR에 SP값 할당

t3 : MAR에 할당된 주소에 해당하는 값을 MBR에 전달

t4 : MBR에 할당된 값을 PC값 전달

예시 7 : 중첩 서브루틴, 다중 서브루틴

(1) : 340이 실행되면서 다음 실행되어야할 341을 스택에 넣는다. 또한 SP가 다음 스택주소인 998로 설정

(2) : 722가 실행되면서 다음 실행되어야할 723을 스택에 넣는다. 또한 SP가 다음 스택주소인 997로 설정

(3) : 결과를 반환하면서 스택에서 723을 뺀다. 또한 다시 SP가 998로 설정된다.

-> 위의 과정을 규칙삼아 반복

3-4. 인터럽트 사이클

- 실행 주기가 완료되면 인터럽트가 발생했는지 체크

- 발생시 인터럽트 사이클 실행

인터럽트 사이클

4. 파이프 라이닝

제어장치의 기본 수행 순서 (순차적 진행)

파이프 라이닝 기술로 실행

- 명령 한개를 여러 단계로 나누어 각각을 독립적인 장치에서 동시에 실행하는 기술

5단계 파이프 라이닝

- 각각의 단계를 S1~S5로 표현한 5단계 파이프 라이닝 기술

- 실행시간 훨씬 단축

1단계 : 메모리에서 명령어 인출

2단계 : 명령어를 해독하고 명령어 형태를 결정하며 필요한 피연산자 결정

3단계 : 레지스터 또는 메모리에서 피연산자 결정

4단계 : 명령어 연산 수행

5단계 : 결과를 레지스터에 저장

시간에 단축 예시

4-1. 파이프라이닝의 문제 1 : 데이터 해저드 (Data Hazards)

- 앞의 명령결과가 다음에 이어질 명령결과에 영향을 주는 경우(데이터 의존성) 파이프 라인 시스템에서 문제가 발생

종류

- WAW, WAR 해저드 : 레지스터를 관련 없는 레지스터로 바꾸어 사용함으로써 해당 해저드 해결

(Write After Write, Write After Read)

- RAW 해저드

RAW 해저드 예시

- 해결 방법

- 레지스터에 결과가 저장되기 전에 해당 결과를 다음 명령어에 직접 전달하는 데이터 포워딩

- 버블을 명령어 사이에 끼워넣어 프로그램 실행을 1단계에서 2단계 지연시키는 방법

4-2. 파이프라이닝의 문제 2 : 제어 해저드 (Control Hazards)

- 파이프라인 CPU 구조의 분기 명령이 실행될때 발생하는 문제를 의미.

- 즉, 이미 파이프라인에 적재되어 실행되고 있는 명령어들이 더이상 실행할 필요가 없어지는 경우

- 전체 프로그램 속도 저하의 원인이 된다.

해결 방법

- 지연슬롯을 넣고 분기 목적지 주소를 계산하는 과정을 파이프라인 속에 넣는 것

(지연슬롯 : NOP나 분기명령과 관계없는 명령어를 끼워넣는 것, 컴파일러나 프로그래머가 프로그램 순서를 바꾸는 것)

- 분기 예측 알고리즘 이용

4-3. 파이프라이닝의 문제 3 : 구조적 해저드 (Structural Hazards)

- 서로 다른 파이프에서 동시에 컴퓨터 내의 장치를 사용하려고 할 때 발생하는 문제를 의미.

예시 : 명령어 인출, 오퍼랜드 인출 동시 실행(버스, 메모리에서 충돌), ALU 동시에 사용

해결 방법

(인출 문제 해결)

- 하버드 구조를 사용 : 메모리를 명령어 메모리와 데이터 메모리로 분리해서 사용하는 구조

- 분리 캐시를 사용하여 충돌 회피 : 캐시를 명령어 캐시와 데이터 캐시로 분리해서 사용하는 방식으로 캐시 미스 발생시 해결이 안됨.

(동시에 장치 접근 해결)

- 장치를 하나 더 사용(예 : ALU 2개 사용)

슈퍼 스칼라

- 하나의 프로세스 안에 2개 이상의 파이프 라인 탑재

- 명령어 인출 장치가 명령어를 쌍을 지어 가져오고 각각의 파이프라인에 배치하며 각각의 파이프라인은 서로다른 장치(ALU 등)를 사용하는 구조

- 쌍을 이룬 두 명령어는 서로 의존하지 않아야 함.

- 하드웨어를 추가하여 실행 도중에 충돌을 감지 및 제거

실행 규칙

1. 명령어 한쌍이 동시 병렬 실행 가능한지 파악

2. 불가능한 경우 첫번째 명령어만 실행

3. 두번째 명령어는 다음 명령어와 함께 짝을 지어 실행

4. 명령어는 항상 순서대로 실행

'CS Knowledge > Computer Structure' 카테고리의 다른 글

| Computer Structure - Sub Memory (0) | 2023.06.18 |

|---|---|

| Computer Structure - Memory (1) | 2023.06.14 |

| Computer Structure - CPU(2) (0) | 2023.04.18 |

| Computer Structure - CPU(1) (0) | 2023.04.17 |

| Computer Structure - Digital Logic Circuits(2) (0) | 2023.04.17 |